Panuje powszechna zgoda (1,

2), że z powodu fundamentalnych ograniczeń fizycznych przemysł mikroelektroniczny zbliża się do końca swojej obecnej mapy drogowej (

1) miniaturyzacji obwodów komputerowych opartych na litograficznie wytwarzanych tranzystorach masowo-krzemowych (Si).

W związku z tym wiele wysiłku zainwestowano w dziedzinie nanoelektroniki w celu opracowania nowatorskich, alternatywnych urządzeń elektronicznych w skali nanometrów i technologii wytwarzania, które mogłyby służyć jako potencjalne drogi dla coraz gęstszych i bardziej wydajnych systemów, aby umożliwić dalszy postęp technologiczny i ekonomiczny (

3-17).

Wysiłki te zaowocowały prostymi obwodami nanoelektronicznymi (

3-5,

8-17) i bardziej złożonymi systemami obwodów (

6,

7), które wykorzystują nowe nanomateriały, ale nie są zintegrowane w skali nanometrów. W związku z tym zbudowanie nanokomputera, który wykracza poza ostateczne ograniczenia skalowania konwencjonalnej elektroniki półprzewodnikowej, było głównym celem dziedziny nanonauki i długoterminowym celem przemysłu komputerowego.

Maszyna skończona (FSM) jest reprezentacją nanokomputera, ponieważ jest podstawowym modelem taktowanych, programowalnych obwodów logicznych (

18,

19) i integruje kluczowe elementy arytmetyczne i logiczne pamięci. Ogólnie rzecz biorąc, FSM musi utrzymywać swój stan wewnętrzny, modyfikować ten stan w odpowiedzi na bodźce zewnętrzne, a następnie na tej podstawie wysyłać polecenia do środowiska zewnętrznego (

18,

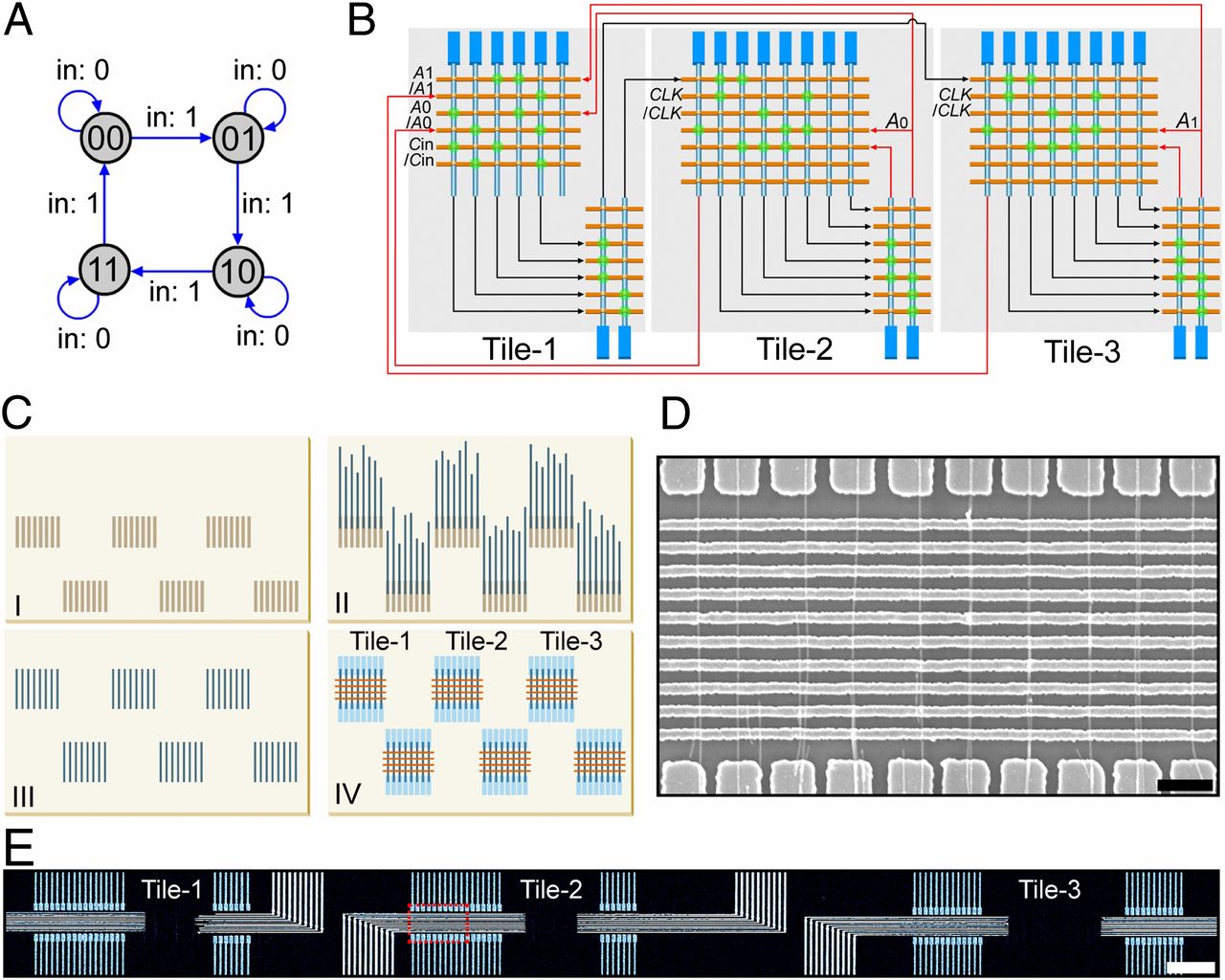

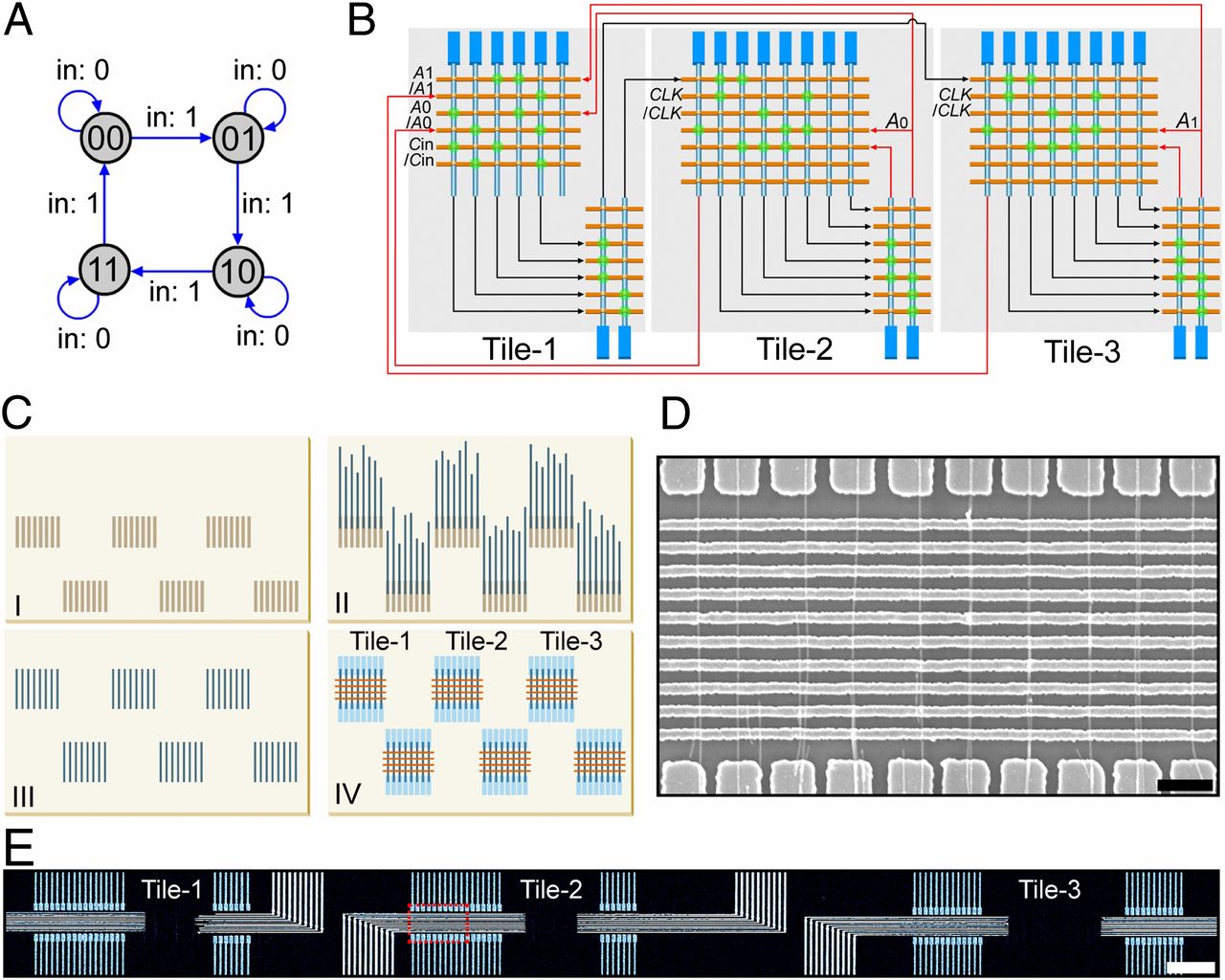

19). Podstawowy diagram przejścia stanu dla 2-bitowego czterostanowego FSM badanego w naszej pracy (

ryc. 1A) podkreśla cztery binarne reprezentacje "00", "01", "10" i "11" oraz przejście z jednego stanu do drugiego wyzwalane przez binarny sygnał wejściowy, "0" lub "1". Większe, bardziej złożone FSM mogą być konstruowane przy użyciu dłuższych reprezentacji binarnych.

Wcześniejsze wysiłki przyniosły elementy obwodu, które wykonują proste funkcje logiczne przy użyciu niewielkiej liczby pojedynczych urządzeń nanoelektronicznych (

8-17), ale daleko im do wykazania kombinacji elementów arytmetycznych i rejestrowych wymaganych do realizacji FSM.

W szczególności integracja różnych funkcjonalnych elementów obwodów wymaga zdolności do wytwarzania i precyzyjnego organizowania systemów obwodów, które łączą dużą liczbę adresowalnych urządzeń elektronicznych w skali nanometrowej w łatwo rozszerzalny sposób. W rezultacie wdrożenie nanoelektronicznego FSM (nanoFSM) poprzez oddolny montaż indywidualnie adresowalnych urządzeń nanoskalowych znacznie wykracza poza stan techniki. Ponadto stanowi ogólną lukę między obecnymi obwodami jednojednostkowymi a architekturami modułowymi w celu zwiększenia liczby złożonych i funkcjonalnych systemów nanoelektronicznych (

8,

20–

24). Poniżej opisujemy, w jaki sposób pokonujemy powyższe wyzwania w zakresie projektowania, montażu i wytwarzania obwodów w celu realizacji nanoFSM w programowalnej architekturze wielopłytkowej, która zapewnia również ogólny paradygmat dla dalszych kaskadowych systemów nanoelektronicznych od dołu do góry.

Wyniki i dyskusja

Aby zrealizować nanoFSM, przyjmujemy oddolną strategię kompatybilną przy użyciu wspólnych modułów obwodów lub płytek, które są ze sobą połączone i zaprogramowane dla różnych funkcji logicznych (

21,

22). Ta strategia kontrastuje z konwencjonalnymi projektami obwodów, które wymagają różnych układów dla różnych elementów logicznych. W kontekście tego oddolnego paradygmatu nasza architektura nanoFSM łączy trzy programowalne płytki nanoprzewodowe (

rys. 1B). Po wytworzeniu wspólne płytki lub moduły są rozróżniane przez programowanie, przy czym kafelek-1 jest zaprogramowany do wykonywania operacji arytmetycznych, a kafelek-2 i kafelek-3 są zaprogramowane tak, aby działały jako elementy rejestru odpowiednio dla pierwszej i drugiej cyfry stanu. Każda płytka na

rys. 1B składa się z dwóch programowalnych macierzy tranzystorów nanoprzewodowych, gdzie każdy punkt przecięcia w macierzach odpowiada programowalnemu węzłowi tranzystorowemu o stanie aktywnym (tranzystor) lub nieaktywnym (rezystor). Dane wyjściowe pierwszej tablicy służą jako dane wejściowe do drugiej tablicy, dzięki czemu dwupoziomowa struktura logiczna NOR każdej płytki może być zaprogramowana tak, aby uzyskać pełną logikę Boole'a (

21,

22), a tym samym niezbędne elementy arytmetyczne i rejestrowe nanoFSM.

Trzypłytkowa konstrukcja FSM (rys.

1B) stanowi bardzo znaczący krok naprzód w złożoności w porównaniu z poprzednimi pracami (

8-17), biorąc pod uwagę dużą liczbę pojedynczych nanoprzewodów, które muszą być zorganizowane w wydajny i skalowalny sposób oraz rygorystyczne wymagania dotyczące poszczególnych urządzeń logicznych w odniesieniu do dopasowania napięcia wejściowego / wyjściowego (I / O) i kontroli nad progową zmiennością napięcia.

Stanowi również eksperymentalną implementację oddolnej architektury obwodów wielopłytkowych lub modułowych (

8,

20–

24).

Dokonaliśmy ogólnego przełomu w organizacji oddolnej, wdrażając unikalną deterministyczną metodologię wytwarzania (rys.

1C i rys. S1), który umożliwia zorientowane na projektowanie wytwarzanie nanoFSM z elementów w nanoskali powzrostowej. Nasze podejście obejmuje jeden początkowy etap modelowania, przy czym wszystkie kolejne kroki są rejestrowane w tym początkowym wzorcu, w tym montaż i wzajemne połączenie poszczególnych elementów nanoprzewodów w projekcie nanoFSM z trzema płytkami / sześcioma tablicami. Po pierwsze, dyskretne okresowe miejsca kotwienia są definiowane na podstawie projektu obwodu trójpłytkowego (rys.

1 C, I i rys. S1). Po drugie, nanoczesanie (

25,

26) nanodrutów germanu (Ge) / rdzenia / powłoki Si (

27) daje nanodruty zakotwiczone w każdym miejscu i wyrównane wzdłuż kierunku czesania (

rys. 1 C, II i

ryc. S1 A i B oraz

rys. S2). Po trzecie, boczne układy okresowe nanodrutów są przycinane do początkowo wzorzystych miejsc kotwiczenia (rys.

1 C, III i rys. S1 A i C). Po czwarte, styki elektryczne są wykonywane poprzez rejestrację w początkowych miejscach kotwienia (oś

x) i przyciętej długości (oś

y) bez rejestracji nanoprzewodów (rys.

1 C, IV i rys. S1D).

Obwód nanoFSM i chip zostały uzupełnione przez osadzanie warstw dielektrycznych, metalowych linii bramek i interkonektów do padów I/O do pomiarów (

materiały i metody). Obraz z skaningowego mikroskopu elektronowego (SEM) przedstawiający macierz poprzeczną (rys. 1

D) podkreśla wysoką wierność 10 par elektrod o równym skoku 1 μm łączących się z każdym z dobrze wyrównanych i okresowych nanodrutów w macierzy. Wysoki stopień wyrównania we wszystkich macierzach zapobiega krzyżowaniu się sąsiednich nanoprzewodów, co ma kluczowe znaczenie dla uzyskania jednolitej odpowiedzi bramki w węzłach krzyżowych. Skupienie się na ogólnej strukturze nanoFSM (

rys. 1E) ujawnia dodatkowe kluczowe cechy. Po pierwsze, regularne linie I/O w wyniku niemal deterministycznego montażu pozwalają na rozplanowanie i późniejszy montaż obwodu z trzema płytkami / sześcioma układami zgodnie z naszym projektem trójpłytkowym w porównaniu z typowym projektem pomontażowym (

9-16) (po rejestracji nanoprzewodów). Po drugie, osiągnięto wysoką wydajność urządzeń jednonanoprzewodowych: dla 72 par styków wykonanych w sześciu macierzach 43 (60%) stanowiły urządzenia jednonanoprzewodowe, a pozostałe podwójne nanoprzewody (22%) i wolne miejsca pracy (18%). Początkowy projekt obwodu uwzględniał tę wydajność, włączając wystarczające styki, tak aby każda płytka zawierała wystarczającą liczbę urządzeń jednonanoprzewodowych dla rzeczywistego obwodu. W przypadku jeszcze większych obwodów kafelkowych można zintegrować peryferyjne elementy logiczne routingu, aby uzyskać systematyczną architekturę poprzeczną odporną na defekty (

28).

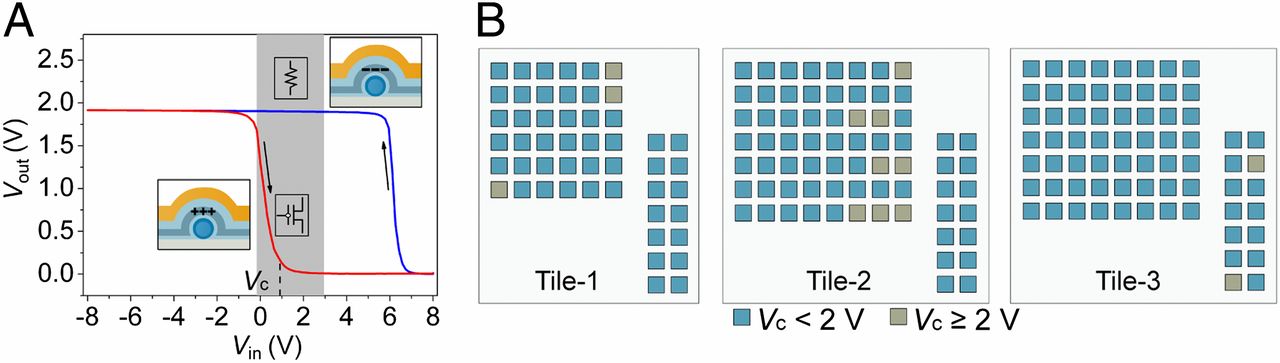

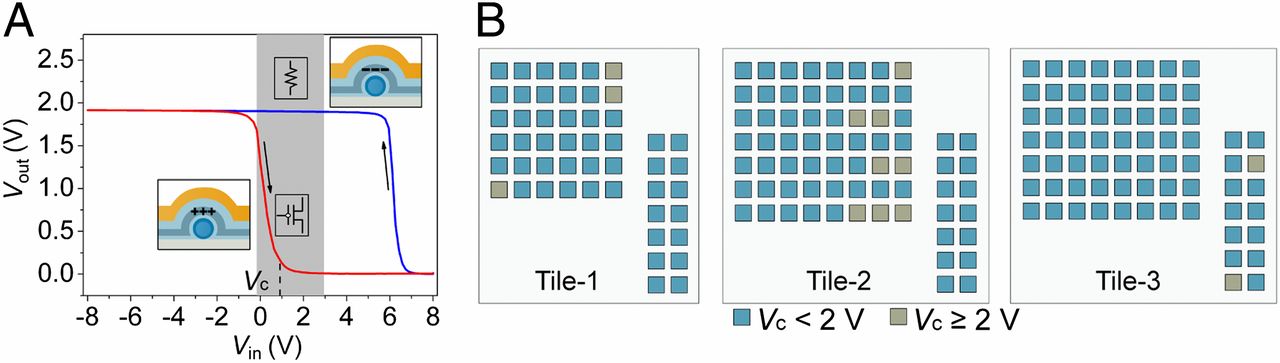

Wydajność pojedynczego nanoprzewodu, skok nanoprzewodów i rozstaw linii bramki (400 nm) dają 1,8 tranzystora / μm2 lub 1,8 × 108/centymetr2, co najmniej trzykrotny wzrost gęstości w porównaniu z innymi strategiami projektowania pomontażowego (9, 10, 13, 16). Zauważamy, że 10-krotna poprawa wyrównania nanoprzewodów i 10-krotna redukcja gęstości porażek (np. Krzyżowanie nanoprzewodów) przez nanoczesanie (25) w porównaniu z typowymi metodami montażu druku ścinanego stosowanymi wcześniej (16) umożliwiają zarówno wzrost gęstości obwodu, jak i obwodów wielopłytkowych w tej pracy. Ostatnie, regularne linie I/O nanoFSM (rys. 1E) ulegają fan-out (rys. S3) w celu uzyskania ok. 4 × 4 mm2 Chip z 204 płytkami kontaktowymi, które łączą się z kartą sondy w celu przetestowania. NanoFSM (rys. 1 B) wymaga rozległych przepływów sygnału wewnątrz- i intertile, które wymagają ścisłego dopasowania napięcia I / O węzłów tranzystorowych w gotowych strukturach trójpłytkowych (rys. 1 E). W związku z tym scharakteryzowaliśmy wyjście napięciowe (Vna zewnątrz) w porównaniu z napięciem wejściowym (Vw) charakterystykę wszystkich poszczególnych węzłów w nanoFSM skonfigurowanych jako falowniki (rys. S4). W szczególności Al2O3–ZrO2–Al2O3 warstwę dielektryczną (Materials and Methods) wprowadzoną jako medium zatrzymujące ładunek (16, 29) można zaprogramować z dużym wejściem bramki (np. +8/–8 V) w celu akumulacji/wyczerpania ładunku i tym samym przesunięcia progu tranzystora (rys. S4). W ten sposób przedstawiciel Vna zewnątrz kontra Vw dane pokazują dużą histerezę (rys. 2A), w której węzeł tranzystorowy zachowuje się jak aktywny tranzystor (czerwony) lub nieaktywny rezystor (niebieski) w logicznym zakresie wejściowym 0–3 V (szary obszar) po kroku programowania. Definiujemy napięcie progowe obwodu, Vc, jako wartość Vw przy którym falownik Vna zewnątrz jest zredukowana do 1/10 napięcia zasilania, Vdi ustawia minimalne Vw dla falownika na wyjście 0. Dopasowywanie we/wy wymaga Vc ≤ Vd, tak aby wyjście 1 (∼Vd) jest wystarczające, aby służyć jako wejście do sterowania następnym elementem w obwodzie bez utraty sygnału. Zoptymalizowaliśmy syntezę nanoprzewodów rdzenia / powłoki Ge/Si i etapy wytwarzania urządzeń w celu kontrolowania Vc i spełniają wymagania projektowe Vc ≤ Vd, gdzie głównym wyzwaniem było zminimalizowanie pozytywnych przesunięć Vc w stanie aktywnym i osiągnięcie jednorodności progowej (rys. S5). Co istotne, mapa zmierzonego Vc wartości z trójpłytkowego obwodu nanoFSM (rys. 2B) podkreślają wysoką wydajność węzłów tranzystorowych zdolnych do wzmocnienia lub dopasowania I/O. Dla 190 węzłów tranzystorowych w trzech płytkach, 177 ze 190 węzłów (93%) spełnia Vc ≤ Vd kryteria, ze średnią Vc ±1 SD 0,9 ± 0,7 V przy Vd = 2 V. Na koniec histogram dla tych samych 190 węzłów zaprogramowanych do stanu nieaktywnego (rys. S6) pokazuje, że 100% ma Vc > 3,5 V (Vc ± 1 SD 6,2 ± 0,5 V), który znajduje się poza górnym limitem (3 V) okna logicznego. Zaprogramowano działanie obwodu FSM, które zostało zweryfikowane przez symulacje przed wytworzeniem (rys. S7) jak pokazano na rys. 1B, z A1A0, Cwi CLK reprezentują odpowiednio stan 2-bitowy, wejście sterujące i sygnał zegara. W tej architekturze tile-1 jest skonfigurowany jako półsumator, który oblicza sumowanie A1A0 + Cw. Jego wydajność A′1A′0 jest nowym stanem, w którym A′0 = A0 Cw, A′1 = A1

Cw, A′1 = A1 (A0•Cw), a znaki "" i "•" reprezentują odpowiednio logikę XOR i AND. Obliczone A′

(A0•Cw), a znaki "" i "•" reprezentują odpowiednio logikę XOR i AND. Obliczone A′ 0 oraz A′1 wartości są wprowadzane do kafli-2 i kafelka-3, które są skonfigurowane jako przerzutniki D (30) (DFF). DFF rejestrują nowy stan na krawędzi narastającej zsynchronizowanego CLK, a następnie ten zarejestrowany stan jest natychmiast przekazywany z powrotem jako dane wejściowe do sumatora w celu obliczenia stanu następnego poziomu. Najpierw scharakteryzowaliśmy wydajność trzech "komponentowych" płytek w nanoFSM; wyniki te wykazały, że półsumator i DFF (rys. S8 i rys. S9) wykazał poprawną logikę. Na przykład DFF, który nie został wcześniej zademonstrowany w obwodach oddolnych, obejmuje dwie intratile sprzężenia zwrotnego obejmujące sześć z siedmiu funkcjonalnych nanoprzewodów w obwodzie, a zatem jest znacznie bardziej złożony i wymaga bardziej rygorystycznego dopasowania I / O i jednorodności tranzystora niż zademonstrowane obwody z pojedynczymi pętlami sprzężenia zwrotnego (14-16). Spełnienie rygorystycznego dopasowania I/O znajduje odzwierciedlenie w dokładnym przepływie logicznym i dopasowaniu wyjścia Q do wejścia D i sygnału zegarowego CLK (rys. S9B). Ponadto zaprogramowany DFF nie wykazał wyraźnej degradacji po 10 godzinach w środowisku otoczenia (rys. S9C), wykazując w ten sposób solidność i niezmienność zaprogramowanych płytek.

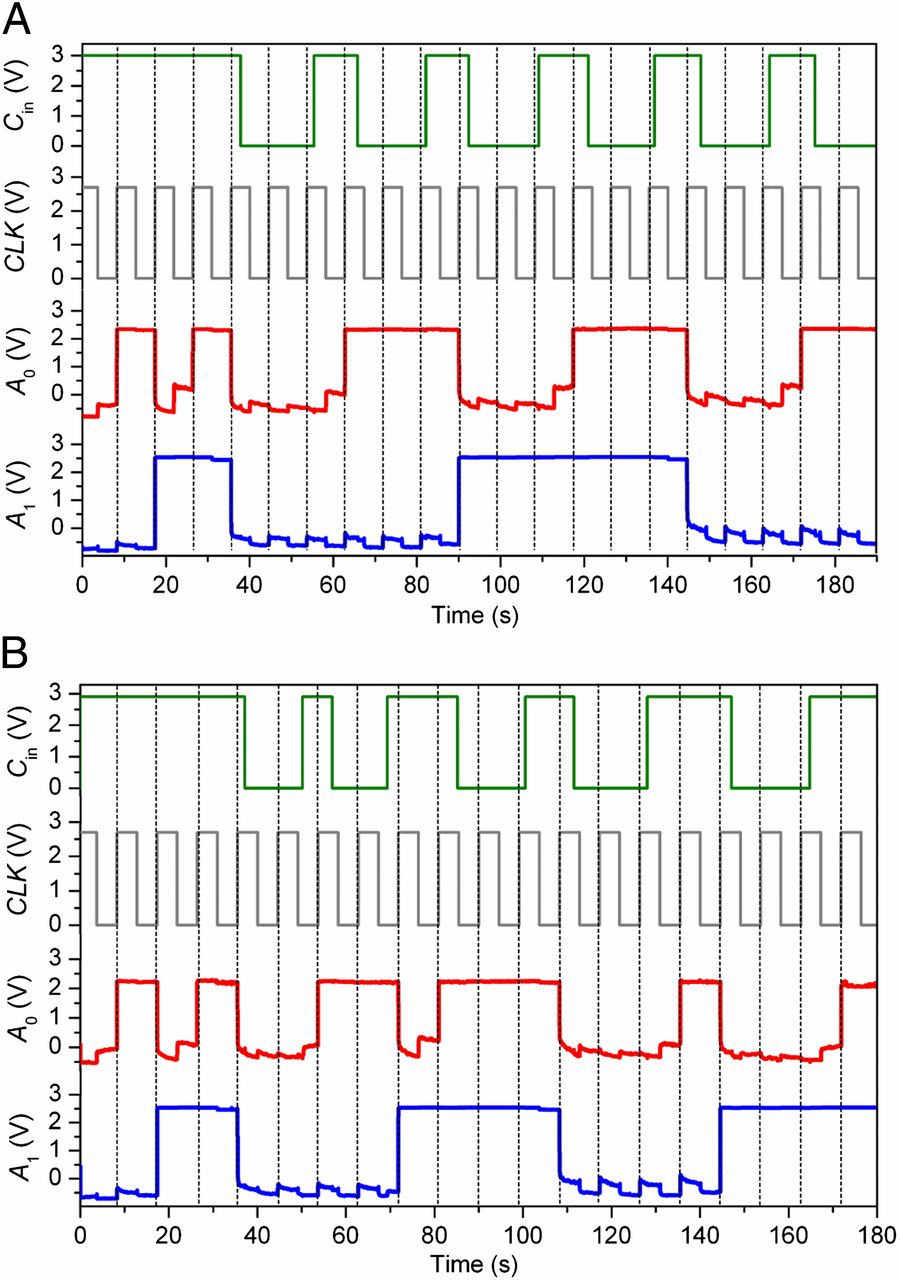

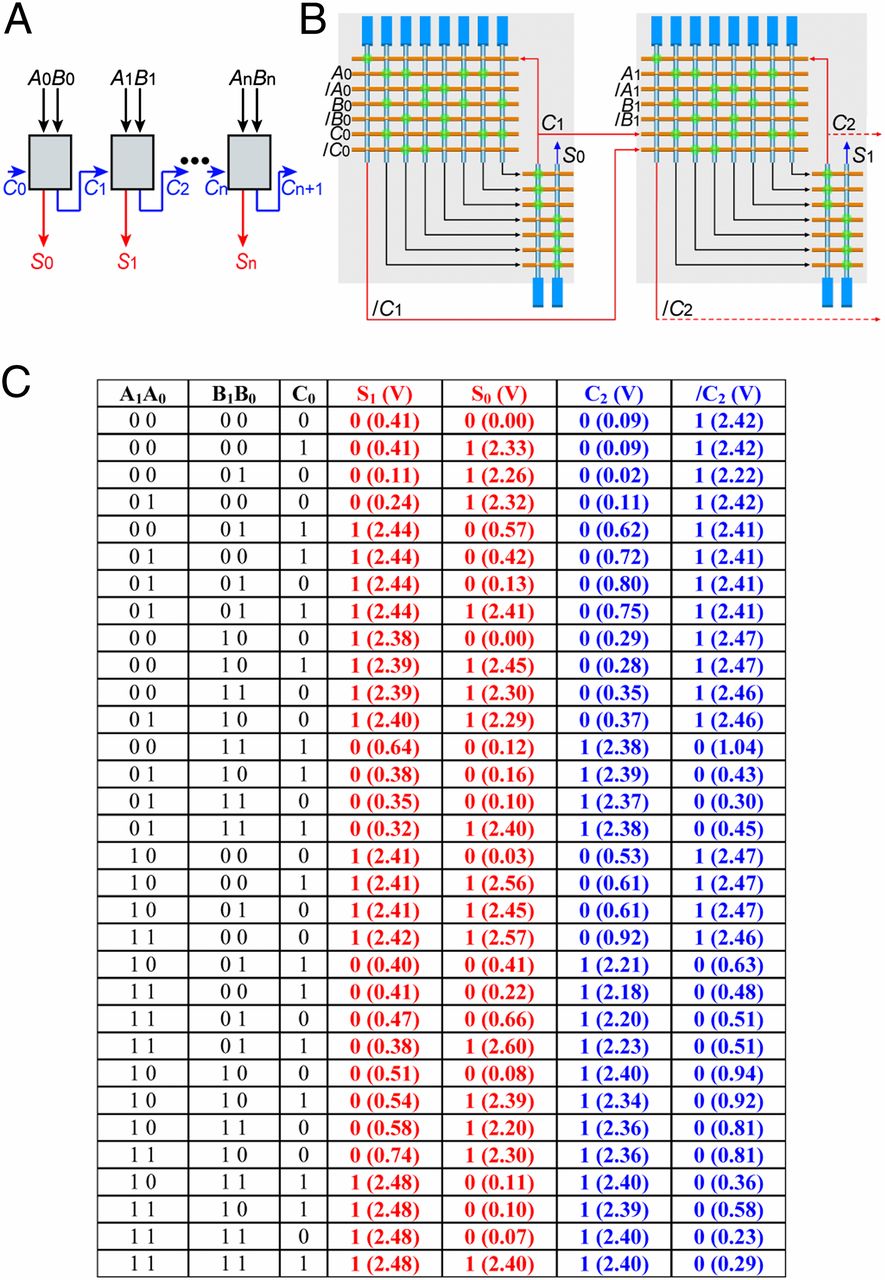

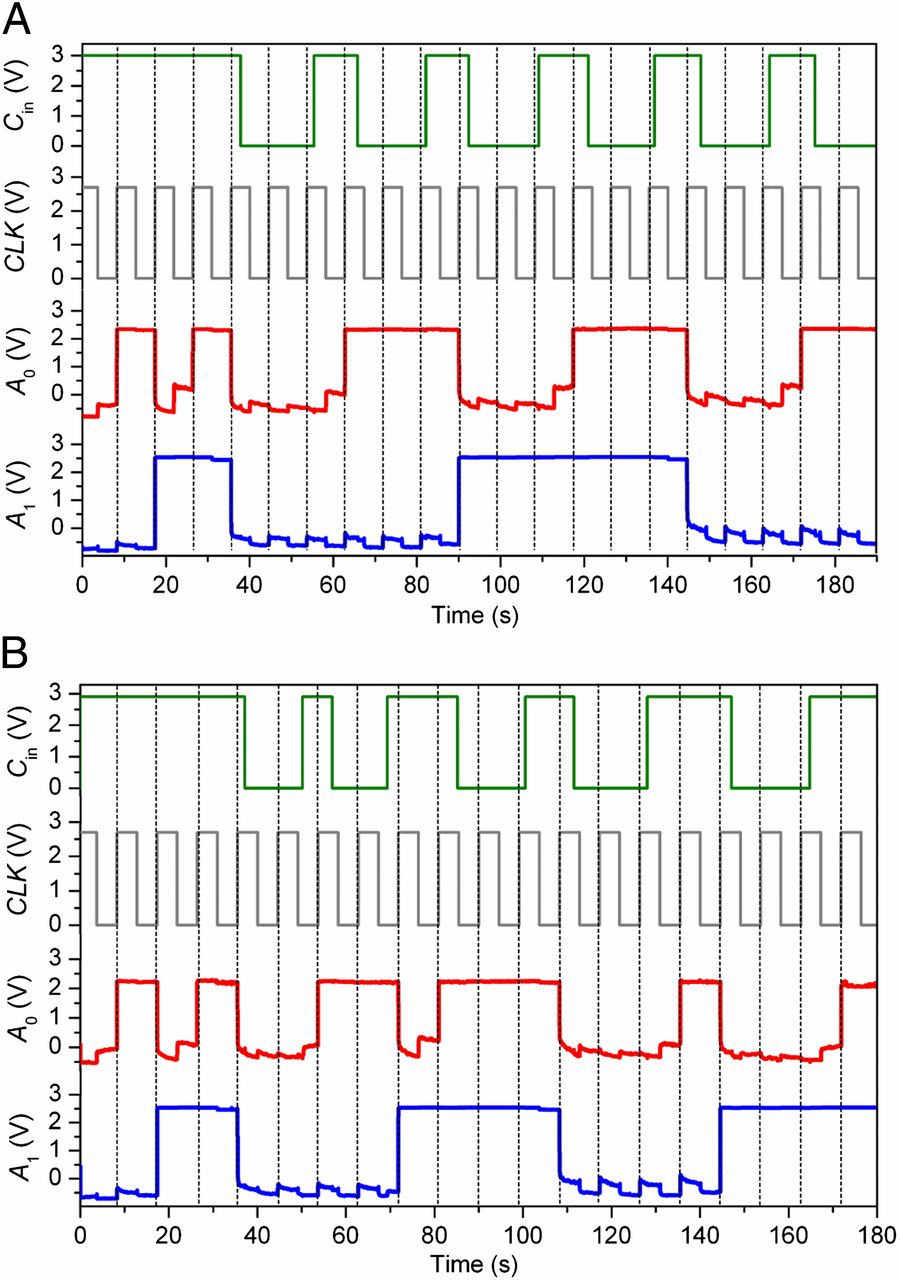

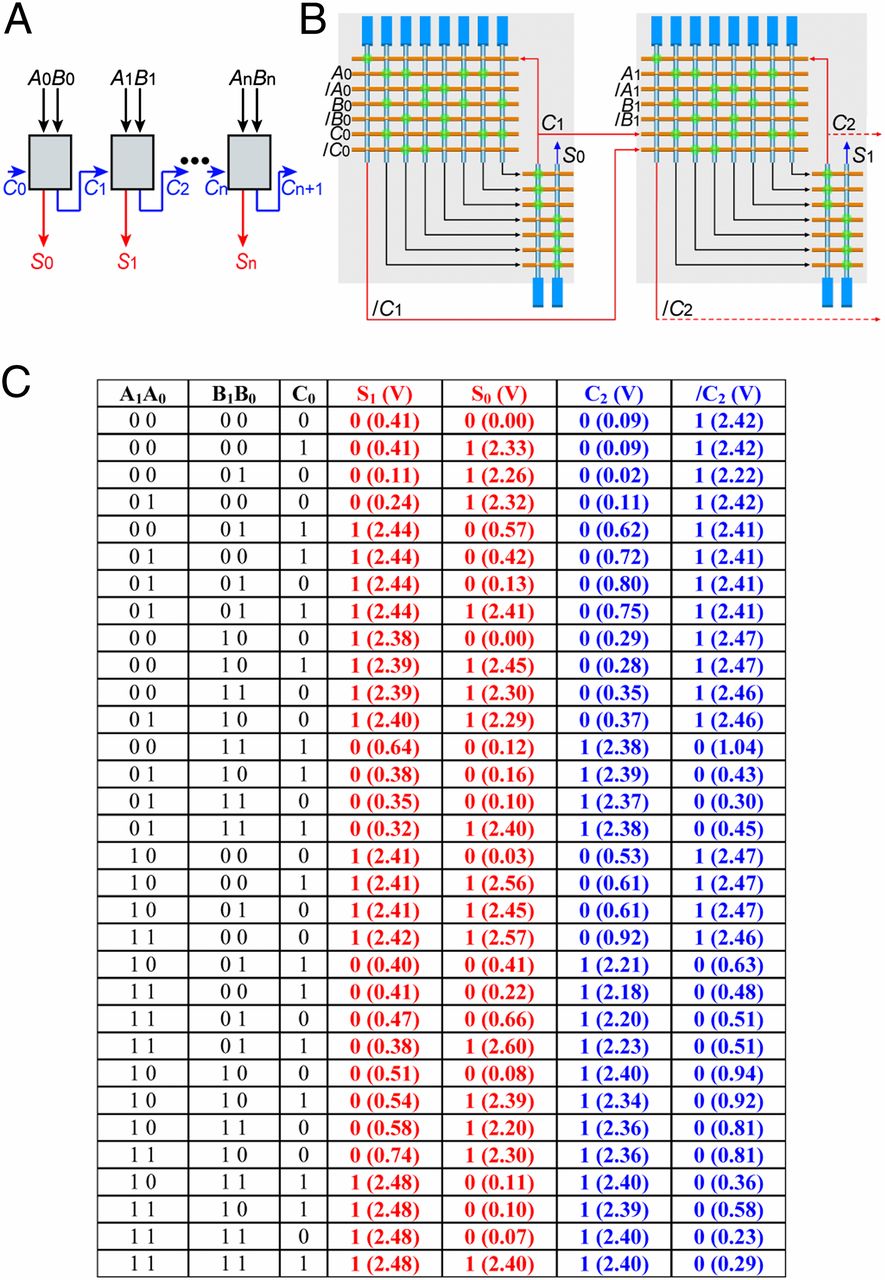

0 oraz A′1 wartości są wprowadzane do kafli-2 i kafelka-3, które są skonfigurowane jako przerzutniki D (30) (DFF). DFF rejestrują nowy stan na krawędzi narastającej zsynchronizowanego CLK, a następnie ten zarejestrowany stan jest natychmiast przekazywany z powrotem jako dane wejściowe do sumatora w celu obliczenia stanu następnego poziomu. Najpierw scharakteryzowaliśmy wydajność trzech "komponentowych" płytek w nanoFSM; wyniki te wykazały, że półsumator i DFF (rys. S8 i rys. S9) wykazał poprawną logikę. Na przykład DFF, który nie został wcześniej zademonstrowany w obwodach oddolnych, obejmuje dwie intratile sprzężenia zwrotnego obejmujące sześć z siedmiu funkcjonalnych nanoprzewodów w obwodzie, a zatem jest znacznie bardziej złożony i wymaga bardziej rygorystycznego dopasowania I / O i jednorodności tranzystora niż zademonstrowane obwody z pojedynczymi pętlami sprzężenia zwrotnego (14-16). Spełnienie rygorystycznego dopasowania I/O znajduje odzwierciedlenie w dokładnym przepływie logicznym i dopasowaniu wyjścia Q do wejścia D i sygnału zegarowego CLK (rys. S9B). Ponadto zaprogramowany DFF nie wykazał wyraźnej degradacji po 10 godzinach w środowisku otoczenia (rys. S9C), wykazując w ten sposób solidność i niezmienność zaprogramowanych płytek. Zbadaliśmy przepływ logiczny i wierność nanoFSM dla różnych Cw i sekwencje CLK poprzez ciągłe nagrywanie A0 (v) oraz A1 (V). Po pierwsze, dla stałego wejścia sterującego Cw = 1 (rys. 3 A), stan A1A0 przeszedł pełny okrąg logiczny od 00→01→10→11→00, z każdym przejściem wyzwalanym przez krawędź narastającą CLK. Możliwość pełnej kontroli i blokowania stanu poprzez zmianę Cw jest pokazana dla t = 38–190 s. Na przykład dla Cw = 0 (t = 38–55 s), stan A1A0 = 00 został zablokowany i nie został uruchomiony do następnego poziomu na dwóch kolejnych krawędziach wznoszących CLK (t = ∼45, 54 s). Gdy wejście sterujące zmieniło się na Cw = 1, stan został odblokowany i przeniesiony do A1A0 = 01 na krawędzi narastania CLK (t = ∼63 s). Ta wysoka wierność kontroli jest pokazana dla wszystkich innych stanów 01, 10 i 11, które zostały zablokowane, gdy Cw = 0 i kontynuowane w pętli logicznej, gdy Cw = 1 (t = 66–190 s). Wytrzymałość nanoFSM została następnie przetestowana poprzez wprowadzenie bardziej nieregularnego przebiegu kontrolnego (rys. 3B), podczas którego stany były okresowo blokowane. Na przykład blokada stanu 01 z Cw = 0 (t = 57–69 s) następowało ciągłe przejście od 01→10→11 z Cw = 1 (t = 69–85 s) przed zablokowaniem stanu 11 za pomocą Cw = 0 (t = 85–101 s). Podobny przepływ logiki pokazano dla przejścia z 00→01→10 (t = 111–165 s). Ogólnie rzecz biorąc, pełna wierność logiczna i arbitralna kontrola stanu w tych pomiarach podkreślają udaną implementację kaskadowego obwodu nanoFSM z trzema płytkami. Aby zbadać wykonalność rozszerzenia liczby kaskadowych płytek, przeprogramowaliśmy obwód na 2-bitowy pełny sumator. Ponieważ wielobitowy sumator pełny może być zrealizowany przez szeregowe połączenie 1-bitowych pełnych sumatorów (31) (rys. 4A), to wyjście z kolejnych połączonych ze sobą płytek zapewnia krytyczną miarę możliwości rozszerzenia kaskady. Wysoka wydajność węzłów tranzystorowych zdolnych do dopasowania I/O (rys. 2B) została wykorzystana do przeprogramowania dwóch DFF nanoFSM w taki sposób, że 2-bitowy pełny obwód sumatora zawiera odrębną konfigurację aktywnych węzłów (tj. poza minimalnymi zmianami wymaganymi do realizacji logiki sumatora). W tym kaskadowym obwodzie dwupłytkowym (rys. 4B) każdy 1-bitowy pełny sumator oblicza sumę Sja = Aja Bja

Bja Cja i przenieść Ci+1 = Aja•Bja+Aja•Cja+Bja•Cja

Cja i przenieść Ci+1 = Aja•Bja+Aja•Cja+Bja•Cja (

i = 1, 2; "+" oznacza logikę OR), z obliczonym Ci+1 i uzupełniające /Ci+1 służąc jako wejście do sumatora wyższego bitu. Ogólnie rzecz biorąc, 2-bitowy pełny sumator oblicza sumowanie A1A0 + B1B0 + C0, z S0 oraz S1 pierwsza i druga cyfra sumy i C2 przeniesienie. Co istotne, badanie wartości dla pełnej 32-elementowej tabeli prawdy (rys. 4C) pokazuje, że pełna logika wychodzi dla S0/ 01, C2, oraz /C2 są poprawne, a ich średnie napięcia wyjściowe logiczne 1 2,43 ± 0,03, 2,39 ± 0,12, 2,34 ± 0,08 i 2,43 ± 0,06 V są dobrze dopasowane (nieznacznie zwiększone) w stosunku do wspólnej wartości wejścia logicznego 1, 2,3 V. Wyniki te zdecydowanie potwierdzają wykonalność implementacji pełnych sumatorów >2-bitowych poprzez kaskadowanie większej liczby kafelków. Wnioski

Wielopłytkowe obwody programowalne nanoFSM i 2-bitowe pełne programowalne obwody sumatora zademonstrowane powyżej podkreślają kilka odrębnych cech w porównaniu z poprzednimi obwodami opartymi na elementach zmontowanych od dołu do góry (

8-17).

Po pierwsze, złożoność jest ponad trzykrotna pod względem liczby urządzeń (180 elementów tranzystorowych) w porównaniu z całą poprzednią pracą (

9-17), przy czym gęstość urządzeń w nanoFSM jest również znacznie większa.

Ta złożoność jest dodatkowo zwiększona pod względem funkcjonalności obwodu poprzez włączenie zarówno sekwencyjnych, jak i kombinacyjnych elementów logicznych. Po drugie, praca ta zapewnia konkretną demonstrację integracji płytek i wielu intertile I/O krytycznych dla kaskadowych architektur wielopłytkowych (

8,

20–

24) i ogólnie złożonych obwodów. W szczególności udane taktowanie nanoFSM wymagało ośmiu intertile i intratile sprzężenia zwrotnego z dopasowanymi wartościami I/O, w przeciwieństwie do maksymalnie jednej zademonstrowanej wcześniej w pojedynczych jednostkach funkcjonalnych (

14-16).

Po trzecie, zamiast stosować ograniczoną strategię produkcji oddolnej we wszystkich poprzednich pracach (

9-16), nasza

precyzyjna, deterministyczna, oddolna metodologia wdrożyła zorientowaną na projektowanie strategię wytwarzania obwodów, która odniosła tak duży sukces w konwencjonalnym przemyśle elektronicznym. Podsumowując, uważamy, że wyniki te stanowią znaczący skok w skalowaniu obwodów elektronicznych od dołu do góry. Nasza praca sugeruje wyraźnie, że nanoprocesory ogólnego przeznaczenia (

20-24) mogą zostać zrealizowane w najbliższej przyszłości.